Page 1108 - Informatica dalla A a Z

P. 1108

583

Questa “limitazione” impone il multiplexaggio delle linee indirizzi e dati.

Il BUS di sistema è organizzato in modo tale che alcune linee del BUS dati e del BUS indirizzi

sono condivise.

Nota: Il ciclo di BUS è l’insieme delle fasi usate dalla CPU per comunicare con la memoria,

con un dispositivo di I/O, con l’interrupt controller.

Il processore è costituito da due sottosistemi che operano in modo parzialmente indipen-

dente e asincrono: l’Execution Unit (EU) e il BUS Interface Unit (BIU).

La EU costituisce la parte della CPU che elabora, ed è costituita da:

- registri general purpose (AX, BX, CX, DX);

- registri speciali (PSW o registro dei flag);

- unità di controllo (EU control);

- unità aritmetico-logica (ALU).

La BIU gestisce l’indirizzamento, il prelievo dei dati e delle istruzioni dalla memoria, e inol-

tre gestisce il colloquio con i dispositivi esterni. È costituita da:

- logica di controllo dei bus;

- registri di segmento: CS, DS, SS, ES;

- registro contatore di programma: IP;

- registri puntatore: BP, SP, DI, SI;

- coda delle istruzioni, registro FIFO a 6 byte, in cui vengono memorizzate le istruzioni

da eseguire.

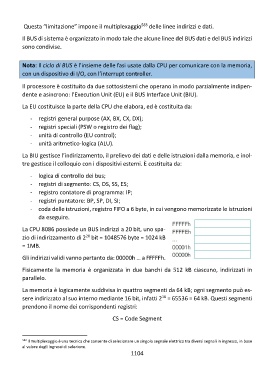

La CPU 8086 possiede un BUS indirizzi a 20 bit, uno spa-

20

zio di indirizzamento di 2 bit = 1048576 byte = 1024 kB

= 1MB.

Gli indirizzi validi vanno pertanto da: 00000h … a FFFFFh.

Fisicamente la memoria è organizzata in due banchi da 512 kB ciascuno, indirizzati in

parallelo.

La memoria è logicamente suddivisa in quattro segmenti da 64 kB; ogni segmento può es-

16

sere indirizzato al suo interno mediante 16 bit, infatti 2 = 65536 = 64 kB. Questi segmenti

prendono il nome dei corrispondenti registri:

CS = Code Segment

583 Il multiplexaggio è una tecnica che consente di selezionare un singolo segnale elettrico tra diversi segnali in ingresso, in base

al valore degli ingressi di selezione.

1104